# MOTOROLA

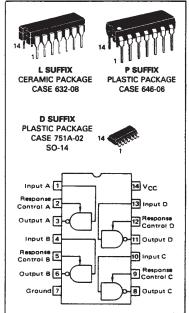

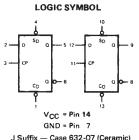

J Suffix — Case 632-07 (Caramic N Suffix — Case 646-06 (Pleatic)

# (S+S P286)

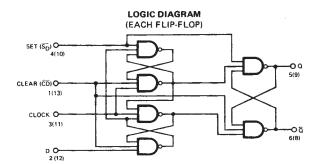

# **SN54LS00 SN74LS00**

QUAD 2-INPUT NAND GATE

LOW POWER SCHOTTKY

## **GUARANTEED OFERATING RANGES**

| SYMBOL | PARAMETER                           |          | MM          | TYP      | MAX         | UNIT     |

|--------|-------------------------------------|----------|-------------|----------|-------------|----------|

| Voc    | Supply Voltage                      | 54<br>74 | 4.5<br>4.75 | 50<br>50 | 5.5<br>5.25 | <b>v</b> |

| TA     | Operating Ambient Temperature Range | 54<br>74 | -55<br>O    | 25<br>25 | 125<br>70   | °C       |

| Юн     | Output Current — High               | 54.74    |             |          | -0.4        | mA       |

| lor    | Output Current Low                  | 54<br>74 |             |          | 4.0<br>8.0  | mA       |

# (M) MOTOROLA

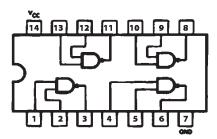

J Suffix — Case 632-07 (Coremic) N Suffix — Case 646-05 (Plactic)

# (S+S P284)

# SN54LSD4 SN74LSD4

**HEX INVERTER**

LOW POWER SCHOTTKY

Related chip: LS175 (p5)

# **MOTOROLA**

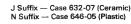

DESCRIPTION - The SN54LS/74LS74A dual edge-triggered flip-flop utilizes Schottky TTL circuitry to produce high speed D-type flip-flops. Each flip-flop has individual clear and set inputs, and also complementary

Information at input D is transferred to the Q output on the positive-going edge of the clock pulse. Clock triggering occurs at a voltage level of the clock pulse and is not directly related to the transition time of the positivegoing pulse. When the clock input is at either the HIGH or the LOW level, the D input signal has no effect.

Dual Flip Flop, like two 7474's (S+S, p312)

# SN54LS74A SN54LS74A

**DUAL D-TYPE POSITIVE EDGE-TRIGGERED FLIP-FLOP**

LOW POWER SCHOTTKY

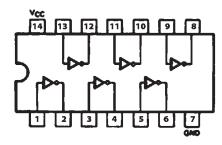

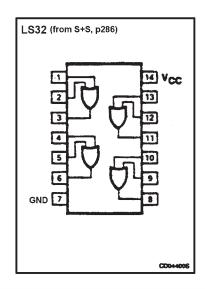

LS86 (from S+S, p288)

### MODE SELECT - TRUTH TABLE

|                   |    | INPUTS     |   | OUT | PUTS |

|-------------------|----|------------|---|-----|------|

| OPERATING<br>MODE | SD | <u>C</u> D | D | Ω   | ā    |

| Set               | L  | Н          | х | н   | L    |

| Reset (Clear)     | н  | L          | х | L   | Н    |

| *Undetermined     | L  | L          | х | H   | н    |

| Load "1" (Set)    | Н  | H          | h | Н   | L    |

| Load "0" (Reset)  | н  | H          | 1 | L   | Н    |

\*Both outputs will be HIGH while both  $\overline{S}_D$  AND  $\overline{C}_D$  are LOW, but the output states are unpredictable if  $\overline{S}_D$  and  $\overline{C}_D$  go HIGH simultaneously. If the levels at the set and clear are near  $V_{IL}$  maximum then we cannot guarantee to meet the minimum level for  $V_{OH}$ .

H, h = HIGH Voltage Level

L, I = LOW Voltage Level X = Don't Care

i, h (q) = Lower case letters indicate the state of the referenced input (or output) one set-up time prior to the LOW to HIGH clock transition

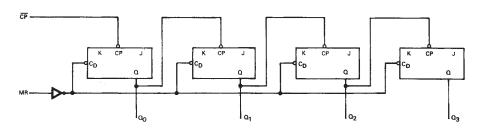

4-Bit Binary Ripple Counter **Product Specification**

## **Logic Products**

#### DESCRIPTION

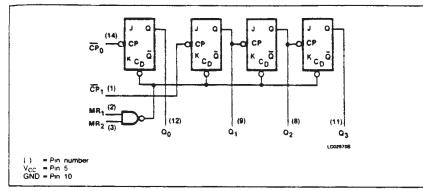

The '93 is a 4-bit, ripple-type Binary Counter. The device consists of four master-slave flip-flops internally connected to provide a divide-by-two section and a divide-by-eight section. Each section has a separate Clock input to initiate state changes of the counter on the HIGH-to-LOW clock transition. State changes of the Q outputs do not occur simultaneously because of internal ripple delays. Therefore, decoded output signals are subject to decoding spikes and should not be used for clocks or strobes.

A gated AND asynchronous Master Reset (MR<sub>1</sub>-MR<sub>2</sub>) is provided which overrides both clocks and resets (clears) all the flip-flops.

Since the output from the divide-by-two section is not internally connected to the succeeding stages, the device may be operated in various counting modes. In a 4-bit ripple counter the output Q<sub>0</sub> must be connected externally to input  $\overline{CP}_1$ .

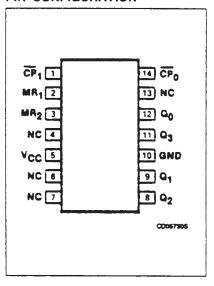

## PIN CONFIGURATION

#### TYPICAL SUPPLY CURRENT TYPE TYPICAL IMAX (TOTAL) 7493 40MHz 28mA 74LS93 42MHz 9mA

# LOGIC DIAGRAM

# **FUNCTION TABLE**

| COUNT                                                                              | OUTPUTS        |    |                |                |

|------------------------------------------------------------------------------------|----------------|----|----------------|----------------|

| COON                                                                               | O <sub>0</sub> | Qı | Q <sub>2</sub> | Q <sub>3</sub> |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15 |                |    |                |                |

NOTE: Output Q<sub>0</sub> connected to input CP<sub>1</sub>.

## MODE SELECTION

| RESET           | INPUTS          | OUTPUTS                                        |   |   |   |  |

|-----------------|-----------------|------------------------------------------------|---|---|---|--|

| MR <sub>1</sub> | MR <sub>2</sub> | Q <sub>0</sub> Q <sub>1</sub> Q <sub>2</sub> Q |   |   |   |  |

| Н               | Н               | L                                              | L | L | L |  |

| L               | H               | Count                                          |   |   |   |  |

| H               | L               | Count                                          |   |   |   |  |

| L               | L               | Count                                          |   |   |   |  |

H = HIGH voltage level L = LOW voitage level X = Don't care

The input count pulses are applied to input CP<sub>0</sub>. Simultaneous divisions of 2, 4, 8 and 16 are performed at the  $\mathsf{Q}_0,\;\mathsf{Q}_1,\;\mathsf{Q}_2$  and  $\mathsf{Q}_3$ outputs as shown in the Function Table.

As a 3-bit ripple counter the input count pulses are applied to input  $\overline{CP}_1$ . Simultaneous frequency divisions of 2, 4 and 8 are available at the Q1, Q2 and Q3 outputs. Independent use of the first flip-flop is available if the reset function coincides with reset of the 3-bit ripple-through counter.

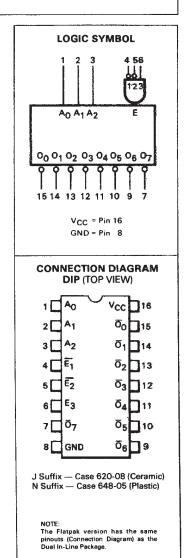

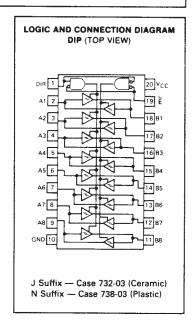

**DESCRIPTION** — The LSTTL/MSI SN54LS/74LS138 is a high speed 1-of-8 Decoder/Demultiplexer. This device is ideally suited for high speed bipolar memory chip select address decoding. The multiple input enables allow parallel expansion to a 1-of-24 decoder using just three LS138 devices or to a 1-of-32 decoder using four LS138s and one inverter. The LS138 is fabricated with the Schottky barrier diode process for high speed and is completely compatible with all Motorola TTL families.

- DEMULTIPLEXING CAPABILITY

- MULTIPLE INPUT ENABLE FOR EASY EXPANSION

- TYPICAL POWER DISSIPATION OF 32 mW

- ACTIVE LOW MUTUALLY EXCLUSIVE OUTPUTS

- INPUT CLAMP DIODES LIMIT HIGH SPEED TERMINATION EFFECTS

| PIN NAME                                                                             | S                                                                    | LOADING (Note a)                 |                                     |  |  |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------|-------------------------------------|--|--|

|                                                                                      |                                                                      | HIGH                             | LOW                                 |  |  |

| A <sub>0</sub> — A <sub>2</sub><br>E <sub>1</sub> , E <sub>2</sub><br>E <sub>3</sub> | Address Inputs Enable (Active LOW) Inputs Enable (Active HIGH) Input | 0.5 U.L.<br>0.5 U.L.<br>0.5 U.L. | 0.25 U.L.<br>0.25 U.L.<br>0.25 U.L. |  |  |

| Ōo — Ō⁊                                                                              | Active LOW Outputs (Note b)                                          | 10 U.L.                          | 5(2.5) U.L.                         |  |  |

#### NOTES:

- a. 1 TTL Unit Load (U.L.) = 40  $\mu$ A HIGH/1.6 mA LOW.

- b. The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74) Temperature Ranges.

FUNCTIONAL DESCRIPTION — The LS138 is a high speed 1-of-8 Decoder/Demultiplexer fabricated with the low power Schottky barrier diode process. The decoder accepts three binary weighted inputs (A<sub>0</sub>, A<sub>1</sub>, A<sub>2</sub>) and when enabled provides eight mutually exclusive active LOW outputs ( $\overline{O}_0$ - $\overline{O}_7$ ). The LS138 features three Enable inputs, two active LOW ( $\overline{E}_1$ ,  $\overline{E}_2$ ) and one active HIGH (E<sub>3</sub>). All outputs will be HIGH unless  $\overline{E}_1$  and  $\overline{E}_2$  are LOW and E<sub>3</sub> is HIGH. This multiple enable function allows easy parallel expansion of the device to a 1-of-32 (5 lines to 32 lines) decoder with just four LS138s and one inverter. (See Figure a.)

The LS138 can be used as an 8-output demultiplexer by using one of the active LOW Enable inputs as the data input and the other Enable inputs as strobes. The Enable inputs which are not used must be permanently tied to their appropriate active HIGH or active LOW state.

#### TRUTH TABLE

|                |                | INP | UTS |                |    |                |                |                | OUT | PUTS           |                |                |                |

|----------------|----------------|-----|-----|----------------|----|----------------|----------------|----------------|-----|----------------|----------------|----------------|----------------|

| Ē <sub>1</sub> | Ē <sub>2</sub> | E3  | Ao  | A <sub>1</sub> | A2 | ō <sub>0</sub> | ō <sub>1</sub> | ō <sub>2</sub> | ō₃  | Ō <sub>4</sub> | Ō <sub>5</sub> | ō <sub>6</sub> | ō <sub>7</sub> |

| н              | ×              | х   | ×   | ×              | х  | н              | н              | н              | н   | н              | н              | Н              | Н              |

| Х              | н              | x   | ×   | ×              | X  | н              | н              | н              | н   | н              | н              | н              | н              |

| X              | ×              | L   | ×   | ×              | x  | н              | н              | H              | H   | н              | н              | н              | н              |

| L              | L              | н   | L   | L              | L  | L              | н              | н              | н   | H              | н              | н              | н              |

| L              | L              | Н   | н   | Ł              | L  | н              | L              | H              | н   | H              | н              | н              | н              |

| L              | L              | н   | L   | н              | L  | н              | H              | L              | н   | н              | н              | н              | н              |

| L              | L              | H   | н   | н              | L  | н              | Н              | н              | L   | н              | н              | н              | н              |

| L              | L              | н   | Ł   | L              | H  | н              | н              | н              | н   | L              | н              | н              | н              |

| L              | L              | н   | н   | L              | H  | н              | н              | H              | н   | н              | L              | н              | H              |

| L              | L              | н   | L   | н              | н  | н              | н              | H              | н   | н              | H              | L              | Н              |

| L              | L              | н   | н   | н              | н  | н              | н              | н              | н   | н              | н              | н              | L              |

H = HIGH Voltage Level

\_ = LOW Voltage Level

X = Don't Care

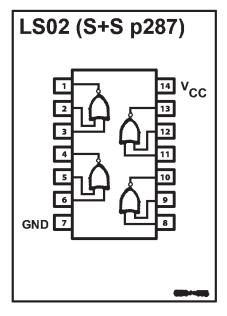

(S+S p327)

# SN54LS138 SN74LS138

1-OF-8-DECODER/ DEMULTIPLEXER

LOW POWER SCHOTTKY

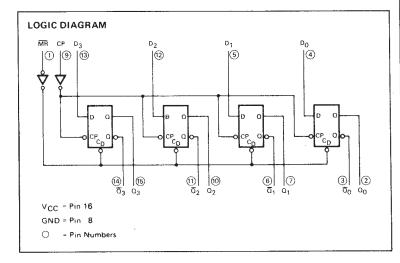

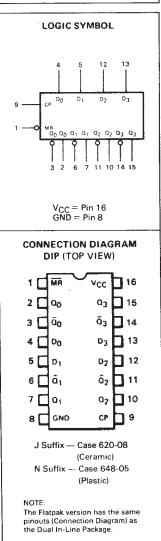

**DESCRIPTION** — The LSTTL/MSI SN54LS/74LS175 is a high speed Quad D Flip-Flop. The device is useful for general flip-flop requirements where clock and clear inputs are common. The information on the D inputs is stored during the LOW to HIGH clock transition. Both true and complemented outputs of each flip-flop are provided. A Master Reset input resets all flip-flops, independent of the Clock or D inputs, when LOW.

The LS175 is fabricated with the Schottky barrier diode process for high speed and is completely compatible with all Motorola TTL families.

- EDGE-TRIGGERED D-TYPE INPUTS

- BUFFERED-POSITIVE EDGE-TRIGGERED CLOCK

- CLOCK TO OUTPUT DELAYS OF 30 ns

- ASYNCHRONOUS COMMON RESET

- TRUE AND COMPLEMENT OUTPUT

- INPUT CLAMP DIODES LIMIT HIGH SPEED TERMINATION EFFECTS

| PIN NAMES                                   |                                      | LOADING (Note a) |             |  |  |  |

|---------------------------------------------|--------------------------------------|------------------|-------------|--|--|--|

|                                             |                                      | HIGH             | LOW         |  |  |  |

| $D_0 - D_3$                                 | Data Inputs                          | 0.5 U.L.         | 0.25 U.L.   |  |  |  |

| CP                                          | Clock (Active HIGH Going Edge) Input | 0.5 U.L.         | 0.25 U.L.   |  |  |  |

| MR                                          | Master Reset (Active LOW) Input      | 0.5 U.L.         | 0.25 U.L.   |  |  |  |

| $\sigma^0 - \sigma^3$                       | True Outputs (Note b)                | 10 U.L.          | 5(2.5) U.L. |  |  |  |

| $\overline{\Omega}_0 - \overline{\Omega}_3$ | Complemented Outputs (Note b)        | 10 U.L.          | 5(2.5) U.L. |  |  |  |

#### NOTES:

a. 1 TTL Unit Load (U.L.) = 40 µA HIGH/1.6 mA LOW.

b. The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74) Temperature Ranges.

# SN54LS175 SN74LS175

Related chip: LS74 (p2)

QUAD D FLIP-FLOP

LOW POWER SCHOTTKY

**FUNCTIONAL DESCRIPTION** — The LS175 consists of four edge-triggered D flip-flops with individual D inputs and Q and  $\overline{Q}$  outputs. The Clock and Master Reset are common. The four flip-flops will store the state of their individual D inputs on the LOW to HIGH Clock (CP) transition, causing individual Q and  $\overline{Q}$  outputs to follow. A LOW input on the Master Reset  $(\overline{MR})$  will force all Q outputs LOW and  $\overline{Q}$  outputs HIGH independent of Clock or Data inputs.

The LS175 is useful for general logic applications where a common Master Reset and Clock are acceptable.

# TRUTH TABLE

| Inputs (t # n, MR = H) | Outputs (t | n+1) Note 1 |

|------------------------|------------|-------------|

| D                      | Q          | ā           |

| L                      | L          | Н           |

| н                      | н          | L           |

Note 1: t = n + 1 indicates conditions after next clock.

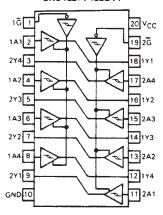

# SN54/74LS244

# OCTAL BUFFER/LINE DRIVER WITH 3-STATE OUTPUTS

LOW POWER SCHOTTKY

SN54LS/74LS244

# SN54LS/74LS244

| INPL  | JTS | OUTOUT |  |  |

|-------|-----|--------|--|--|

| 1G,2G | D   | OUTPUT |  |  |

| L     | L   | L      |  |  |

| L     | Н   | Н      |  |  |

| Н     | Х   | (Z)    |  |  |

$\label{eq:decomposition} \textbf{DESCRIPTION} — The SN54LS/74LS245 is an Octal Bus Transmitter/Receiver designed for 8-line asynchronous 2-way data communication between data buses. Direction Input (DR) controls transmission of Data from bus A to bus B or bus B to bus A depending upon its logic level. The Enable input (<math>\overline{E}$ ) can be used to isolate the buses.

- HYSTERESIS INPUTS TO IMPROVE NOISE IMMUNITY

- 2-WAY ASYNCHRONOUS DATA BUS COMMUNICATION

- INPUT DIODES LIMIT HIGH-SPEED TERMINATION EFFECTS

## TRUTH TABLE

| INP | UTS |                     |  |

|-----|-----|---------------------|--|

| Ē   | DIR | OUTPUT              |  |

| L   | L   | Bus B Data to Bus A |  |

| L   | Н   | Bus A Data to Bus B |  |

| Н   | X   | Isolation           |  |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

# SN54/74LS245

## **OCTAL BUS TRANSCEIVER**

LOW POWER SCHOTTKY

**DESCRIPTION** — The SN54LS/74LS390 and SN54LS/74LS393 each contain a pair of high-speed 4-stage ripple counters. Each half of the LS390 is partitioned into a divide-by-two section and a divide-by-five section, with a separate clock input for each section. The two sections can be connected to count in the 8.4.2.1 BCD code or they can count in a biquinary sequence to provide a square wave (50% duty cycle) at the final output.

Each half of the LS393 operates as a Modulo-16 binary divider, with the last three stages triggered in a ripple fashion. In both the 'LS390 and the LS393, the flip-flops are triggered by a HIGH-to-LOW transition of their CP inputs. Each half of each circuit type has a Master Reset input which responds to a HIGH signal by forcing all four outputs to the LOW state.

- DUAL VERSIONS OF LS290 AND LS293

- LS390 HAS SEPARATE CLOCKS ALLOWING ÷2; ÷2.5, ÷5

- INDIVIDUAL ASYNCHRONOUS CLEAR FOR EACH COUNTER

- TYPICAL MAX COUNT FREQUENCY OF 50 MHZ

- INPUT CLAMP DIODES MINIMIZE HIGH SPEED TERMINATION EFFECTS

| PIN NAN         | MES                              | LOADIN   | LOADING (Note a) |  |  |  |

|-----------------|----------------------------------|----------|------------------|--|--|--|

|                 |                                  | HIGH     | LOW              |  |  |  |

| CP              | Clock (Active LOW going edge)    |          |                  |  |  |  |

|                 | Input to +16 (LS393)             | 0.5 U.L. | 1.0 U.L.         |  |  |  |

| CPO             | Clock (Active LOW going edge)    |          |                  |  |  |  |

| •               | Input to ÷2 (LS390)              | 0.5 U.L. | 1.0 U.L.         |  |  |  |

| CP <sub>1</sub> | Clock (Active LOW going edge)    |          |                  |  |  |  |

| · ·             | Input to ÷5 (LS390)              | 0.5 U.L. | 1.5 U.L.         |  |  |  |

| MR              | Master Reset (Active HIGH) Input | 0.5 U.L. | 0.25 U.L.        |  |  |  |

| $Q_0 - Q_3$     | Flip-Flop outputs (Note b)       | 10 U.L.  | 5(2.5) U.L.      |  |  |  |

#### NOTES

- a. 1 TTL Unit Load (U.L.) = 40  $\mu$ A HIGH/1.6 mA LOW.

- The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74) Temperature Ranges.

Related chip: LS93 (p3)

# SN54LS/74LS390 SN54LS/74LS393

### DUAL DECADE COUNTER; DUAL 4-STAGE BINARY COUNTER

LOW POWER SCHOTTKY

| CONNECTION DIAGRAMS DIP (TOP VIEW)                                                               |

|--------------------------------------------------------------------------------------------------|

| SN54LS/74LS390                                                                                   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                           |

| J Suffix — Case 620-08 (Ceramic)<br>N Suffix — Case 648-05 (Plastic)                             |

| SN54LS/74LS393                                                                                   |

| J Suffix — Case 632-07 (Ceramic) N Suffix — Case 646-05 (Plastic)                                |

| NOTE: The Flatpak version has the same pinouts (Connection Diagram) as the Dual In-Line Package. |

#### SN54LS/74LS393 TRUTH TABLE

| COUNT | OUTPUTS |       |             |                |  |

|-------|---------|-------|-------------|----------------|--|

|       | $0_3$   | $a_2$ | 01          | Q <sub>0</sub> |  |

| 0     |         | L     | L<br>L      | L              |  |

| 1     | L<br>L  | L     | L           | н              |  |

| 2     | L       | L     | н           | L<br>H         |  |

| 3     | L       | L     | н           | H              |  |

| 4     | L       | н     | L           | L              |  |

| 5     |         | н     | L<br>L<br>H | н              |  |

| 6     | L       | ЪΗ.,  | н           | L              |  |

| 7     | L       | Н     | н           | н              |  |

| 8     | H       | L     | L           | L              |  |

| 9     | н       | L     | L<br>L      | н              |  |

| 10    | н       | L     | Н           | Ł              |  |

| 11    | Н       | L     | Н           | Н              |  |

| 12    | Н       | н     | L           | ٢              |  |

| 13    | н       | н     | F           | Н              |  |

| 14    | н       | н     | н           | L              |  |

| 15    | н       | н     | н           | н              |  |

H = HIGH Voltage Level L = LOW Voltage Level FUNCTIONAL DESCRIPTION—Each half of the SN54LS/74LS393 Operates in the Modulo16 binary sequence, as indicated in the  $\div$ 16 Truth Table. The first flip-flop is triggered by HIGH-to-LOW transitions of the CP input signal. Each of the other flip-flops is triggered by a HIGH-to-LOW transition of the Q output of the preceding flip-flop. Thus state changes of the Q outputs do not occur simultaneously. This means that logic signals derived from combinations of these outputs will be subject to decoding spikes and, therefore, should not be used as clocks for other counters, registers or flip-flops. A HIGH signal on MR forces all outputs to the LOW state and prevents counting.

# SN54LS/74LS393 LOGIC DIAGRAM (one half shown)

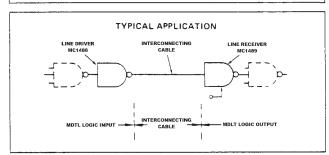

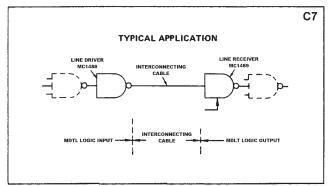

# MC1488

### QUAD LINE DRIVER

The MC1488 is a monolithic quad line driver designed to interface data terminal equipment with data communications equipment in conformance with the specifications of EIA Standard No. RS-232C.

- Current Limited Output ±10 mA typ

- · Power-Off Source Impedance 300 Ohms min

- Simple Slew Rate Control with External Capacitor

- Flexible Operating Supply Range

- Compatible with All Motorola MDTL and MTTL Logic Families  $V_{CC} = +12V, V_{EE} = -12V$

# QUAD MOTL LINE DRIVER RS-232C

SILICON MONOLITHIC INTEGRATED CIRCUIT

# MOTOROLA

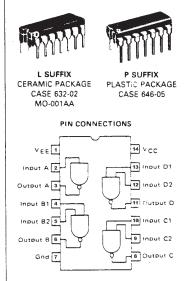

# MC1489 MC1489A

## **QUAD LINE RECEIVERS**

The MC1489 monolithic quad line receivers are designed to interface data terminal equipment with data communications equipment in conformance with the specifications of EIA Standard No. EIA-232C.

- Input Resistance 3.0 k to 7.0 kilohms

- Input Signal Range ± 30 Volts

- Input Threshold Hysteresis Built In

- Response Control

- a) Logic Threshold Shifting

b) Input Noise Filtering

(for RS232->TTL)

VCC = +5V, Response Control is left UNCONNECTED

# **QUAD MDTL LINE RECEIVERS EIA-232C**

SILICON MONOLITHIC INTEGRATED CIRCUIT